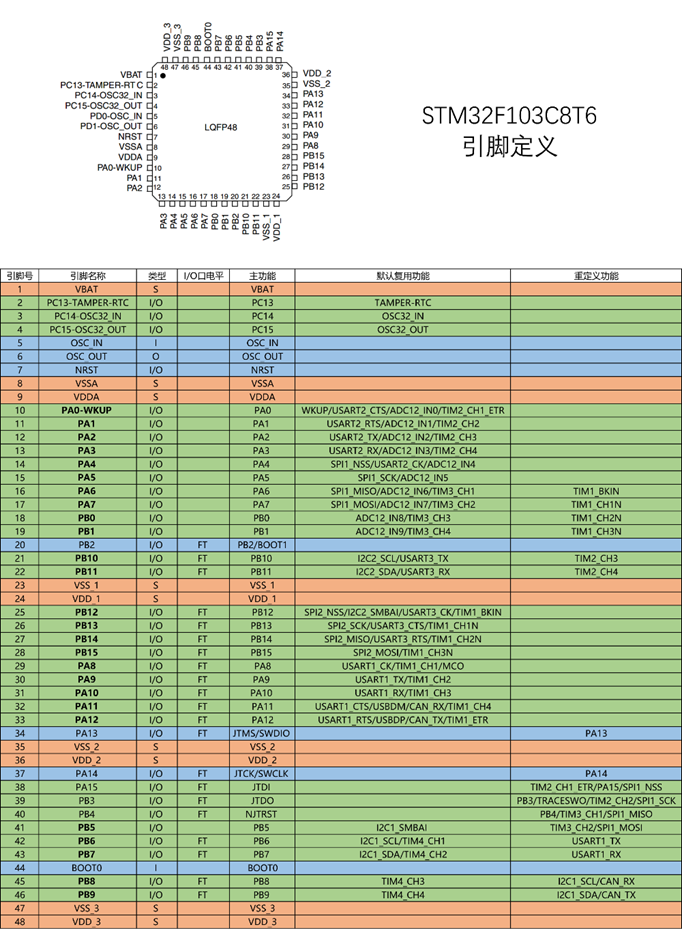

GPIO简介

•GPIO(General Purpose Input Output)通用输入输出口

•可配置为8种输入输出模式

•引脚电平:0V~3.3V,部分引脚(FT)可容忍5V

•输出模式下可控制端口输出高低电平,用以驱动LED、控制蜂鸣器、模拟通信协议输出时序等

•输入模式下可读取端口的高低电平或电压,用于读取按键输入、外接模块电平信号输入、ADC电压采集、模拟通信协议接收数据等

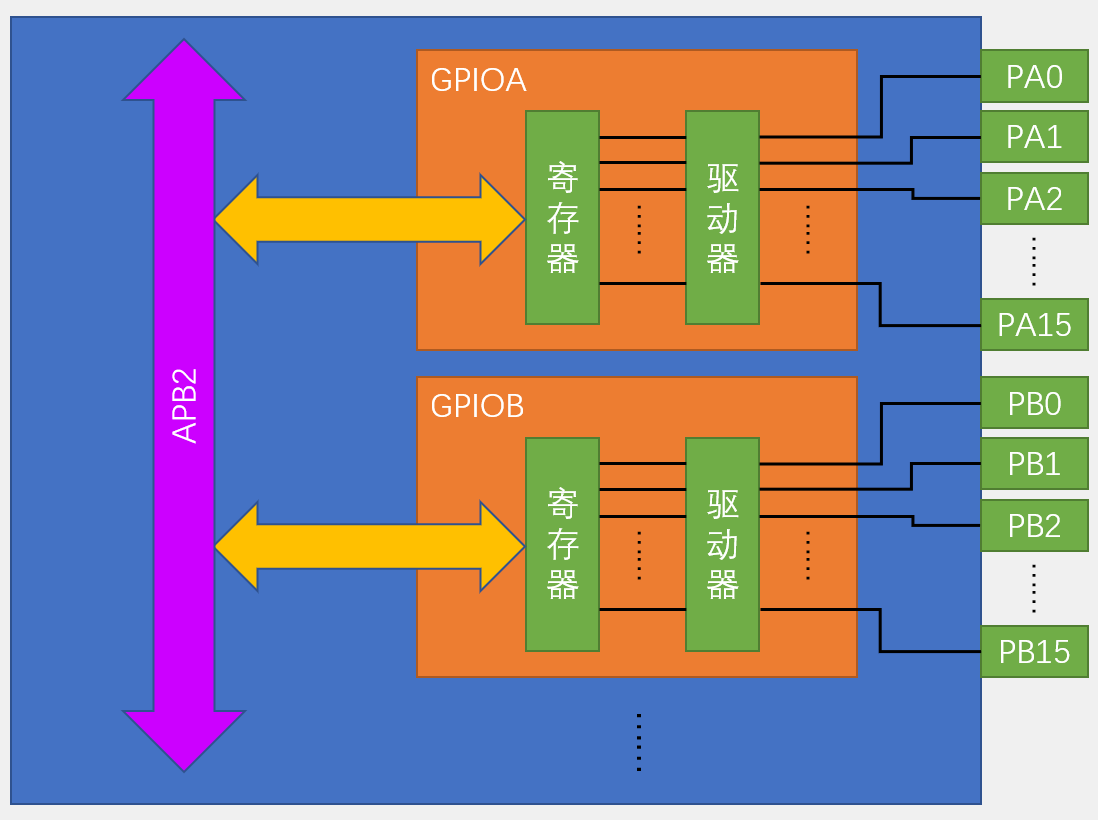

GPIO基本结构

在STM32中,所有GPIO挂载在APB2总线。

每个GPIO有16个引脚,编号从0-15。

在每个GPIO模块中,主要包含寄存器和驱动器,内核通过APB2总线对内核进行读写。

输出寄存器写1,对应的引脚输出高电平,写0,输出低电平。

输入寄存器写1,对应端口目前为高电平,写0,为低电平。

这个寄存器的低16位对应端口,高16位没有使用。

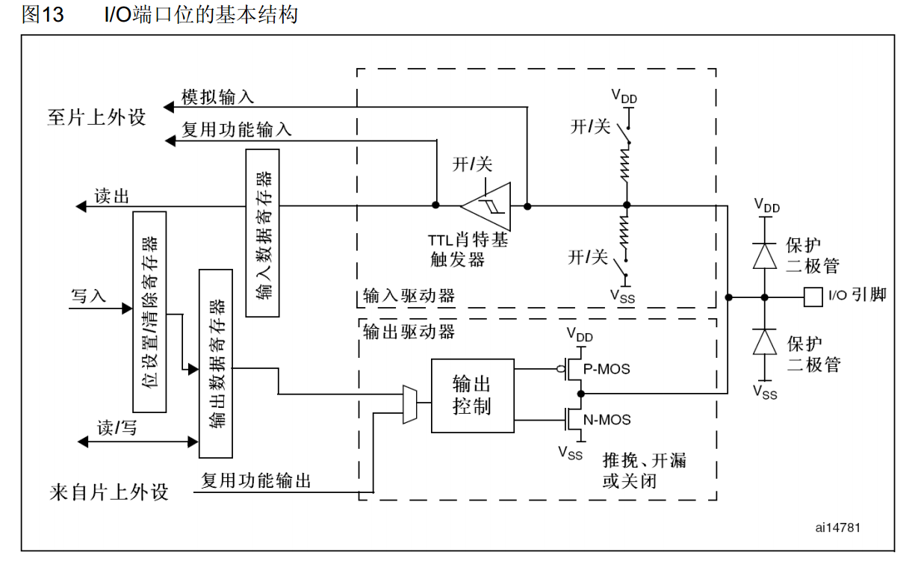

GPIO位结构

上面是输入部分,下面为输出部分。

输入部分:

I/O引脚,两个保护二极管,主要是对输入电压进行限幅的。

输入驱动和器连接上拉电阻和下拉电阻。上拉电阻连接VDD,下拉电阻连接VSS。开关通关程序进行配置。如果上面导通,下面断开,为上拉输入模式,如果上面断开,下面导通,为下拉输入模式,如果都断开,为浮空输入模式。

TTL肖特基触发器(施密特触发器),对输入电压进行整形。如果输入电压大于某一阈值,输出为高电平。输入电压小于某一阈值,输出为低电平。

经过施密特触发器整形的波形,可以直接写入数据寄存器。

上面的2路输入,连接到片上外设。模拟输入,连接到ADC上。为模拟量,在施密特触发器前面。

复用功能输入,连接到其他需要读取端口的外设上。为数字量,在施密特触发器后面。

输出部分

数字部分由输出寄存器或片上外设控制。

选择输出寄存器控制,就是普通的IO口输出。写这个数据寄存器的某一位可以操作端口。

经过输出控制,接到2个MOS管,可以选择推挽、开漏或关闭3种模式。

在推挽输出模式下,P-MOS和N-MOS均有效。

数据寄存器为1时,上管导通,下管断开。输出接到VDD,输出高电平。

数据寄存器为0时,下官导通,上管断开,输出接到VSS,输出低电平。

在推挽输出模式下,STM32对IO口有绝对控制权。

在开漏输出模式下,P-MOS无效,只有N-MOS工作。

数据寄存器为1时,下管断开,输出相当于断开,为高阻模式。

数据寄存器为0时,下管导通,输出直接接到VSS,输出低电平。

这种模式下,只有低电平有驱动能力,高电平没有驱动能力。

开漏模式可以作为通讯协议的驱动方式,比如I2C通信。

开漏模式还可以输出5V电平的信号。

在关闭模式下,两个MOS管都无效,输出关闭,端口的电平由外部信号控制。

GPIO模式

•通过配置GPIO的端口配置寄存器,端口可以配置成以下8种模式

| 模式名称 | 性质 | 特征 |

|---|---|---|

| 浮空输入 | 数字输入 | 可读取引脚电平,若引脚悬空,则电平不确定 |

| 上拉输入 | 数字输入 | 可读取引脚电平,内部连接上拉电阻,悬空时默认高电平 |

| 下拉输入 | 数字输入 | 可读取引脚电平,内部连接下拉电阻,悬空时默认低电平 |

| 模拟输入 | 模拟输入 | GPIO无效,引脚直接接入内部ADC |

| 开漏输出 | 数字输出 | 可输出引脚电平,高电平为高阻态,低电平接VSS |

| 推挽输出 | 数字输出 | 可输出引脚电平,高电平接VDD,低电平接VSS |

| 复用开漏输出 | 数字输出 | 由片上外设控制,高电平为高阻态,低电平接VSS |

| 复用推挽输出 | 数字输出 | 由片上外设控制,高电平接VDD,低电平接VSS |